|

|

|

작성일 : 18-10-01 17:04

작성일 : 18-10-01 17:04

|

글쓴이 :

webmaster

조회 : 13,240

|

|

■ 고속, 미래 메모리 반도체 신뢰성 연구

○ 메모리 설계

- 메모리 Custom 설계

Flip-Flop, SRAM 등 메모리 반도체의 신뢰성 개선을 위해 오류를 완화하거나 강력한 Search 기능을 가진 TCAM을 직접 설계하고 Chip으로 제작하여 개선 여부를 확인합니다.

그림 1. 같은 동작을 하는 Flip-Flop 회로에 대한 최적화 및 오류 완화 Custom 설계

- DRAM 셀 모델링 및 설계

DRAM 메모리의 주요 이슈인 One-Row Hammering, TID Effect에 대한 신뢰성 연구를 위해 TCAD 및 SPICE와 같은 다수의 시뮬레이션 툴 라이선스를 보유하고 있습니다. 시뮬레이션 툴을 이용하여 DRAM 셀 등을 모델링하여 고장이 발생하는 동작을 모의 시뮬레이션 하거나 오류 주입 (Noise injection)을 통해 결과를 분석하고 발생 원인을 찾는 연구를 하고 있습니다.

그림 2. TCAD 시뮬레이션을 이용하여 DRAM의 동작 모델링

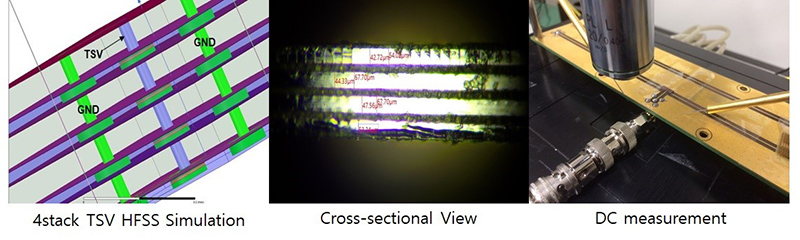

그림 3. TSV 모델링과 측정

- 다양한 Memory Controller 설계

그림 4. RTL 설계 Block Diagram

Intel Altera Quartus를 사용하여 DDR3, DDR4 등의 상용 메모리 테스트에 필요한 다양한 Memory Controller의 custom 설계를 진행하고 있습니다.

그림 5. Intel Altera Quartus Tool

○ 고속 메모리 테스트 시스템 개발

- High Speed 신호에 대한 Signal Integrity

그림 6. 고속 메모리와 컨트롤러 간 I/O 신호 측정

일반적인 고속 메모리와 컨트롤러 사이의 I/O 인터페이스는 그림 6과 같습니다. 드라이버에서 출발한 고속신호는 50옴 임피던스 매칭 선로를 따라 리시버에 도착하며, 임피던스 매칭 정도에 따라 신호왜곡이 발생합니다. SERDES와 같은 아키텍처를 통해 고속의 시리얼 통신이 가능하게 되며, Eye diagram, S-parameter 등 여러 기법을 통해 신호의 품질을 알 수 있게 됩니다.

- FPGA 및 ASIC 설계

DDR3, DDR4, HBM2 등 고속 메모리에 대한 테스트를 위해 Xilinx FPGA, Intel Altera FPGA를 기반으로 하는 테스트 시스템을 개발하였으며 하드웨어의 RTL 설계와 시뮬레이션 검증의 전 과정을 수행하고 있습니다.

그림 7. Full Custom ASIC 설계

- 제어 소프트웨어 개발

다양한 종류의 메모리에 대한 테스트에 능동적으로 대처하기 위하여 테스트 시스템을 제어 및 구동하는 소프트웨어 개발이 필요하게 됩니다. 메모리 테스터의 성능을 개선하고 효율적이고 정확한 테스트 모니터링을 위하여 컴퓨터를 통한 제어가 필수적입니다. 이에 자체 제작된 테스터의 F/W와 외부 제어 프로그램을 개발하여 테스트에 적용하고 있습니다.

그림 8. 메모리 테스트 시스템의 기본 구조

그림 9. 자동화된 테스트 모니터링 결과의 예

○ 극한의 환경에 대한 신뢰성 테스트 수행

- 고온 테스트 환경을 통한 메모리 마진의 영향 분석

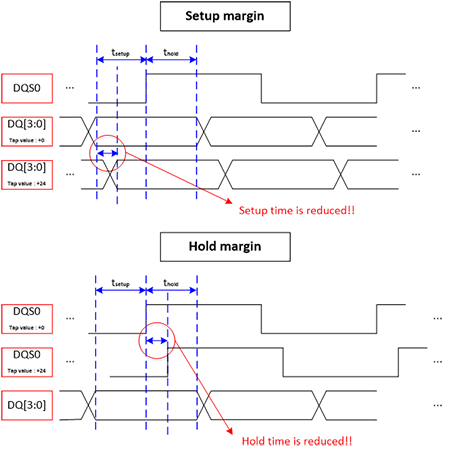

DRAM 각각의 I/O 마진은 온도, 전압, 주파수에 따라 상이한 결과를 나타냅니다. 따라서 우리 연구실에서는 각각의 조건을 제어할 수 있는 DRAM Tester 및 고온제어장치 회로를 제작하였고, 이를 활용하여 조건에 따른 I/O 마진의 변화를 살펴 봄 으로써, DRAM 신뢰성 연구에 활용하고 있습니다.

그림 10. 고온제어장치의 회로부와 샘플단열장치

그림 11. DDR4 DRAM Tester – Implementation

그림 12. 데이터 마진 측정 원리 (Setup / Hold Margin)

- 극저온 테스트 환경 구현 및 실험

DDR3 또는 DDR4 메모리 등의 저온 및 극저온에서의 신뢰성 연구 진행하고 있습니다. 드라이아이스를 사용하여 최저 영하 40 ℃의 저온 환경 구현하였으며, 액체질소를 사용하여 최저 영하 170 ℃의 극저온 환경 또한 구현하여 실험을 진행하고 있습니다.

그림 13. 극 저온 실험을 위한 장비

○ 자연, 우주 방사선에 의한 반도체 영향 테스트 수행

고에너지 입자 혹은 방사선에 의해 반도체는 여러가지 현상 및 동작 오류가 발생합니다. 이를 재현하고 분석하기위해 아래와 같은 국내외 다양한 방사선 조사 시설을 방문하여 연구를 수행하고 있으며 그 결과를 IEEE Journal과 같은 해외 유수 저널논문에 게재되고 있습니다.

- 서울 (Proton, Alpha, Neutron)

- 경주 (Proton)

- 대전 (Thermal Neutron)

○ 미래 메모리 소자에 대한 신뢰성 연구

그림 14. 3D NAND Flash SSD에 대한 신뢰성 실험

Through-Silicon Via(TSV)와 같은 차세대 공정에 대해 발생할 수 있는 문제점과 STT-MRAM, RRAM, 3D XPoint와 같은 미래 반도체 메모리 소자에 대한 연구와 과제를 진행하고 있습니다. 기존의 메모리와 달리 미래 메모리 소자에서 새롭게 발생할 수 있는 문제점을 찾기 위해 극저온, 고온, 전자파, ESD, 방사선 등 다양한 테스트를 할 수 있는 테스트 플랫폼 개발을 수행하고 있습니다.

그림 15. Intel과 Micron에서 개발한 차세대 비휘발성 메모리 3D XPoint

■ System Level에서부터 Packaging Material까지

○ System Level 방사선 영향 연구

메모리 소자 뿐만 아니라, 스마트폰과 같은 복잡한 시스템을 대상으로 방사선을 조사하여 이에 대한 영향을 연구하고 있습니다.

그림 16. 스마트폰에 대한 중성자 조사 실험

○ Packaging Material에서 방출되는 알파

IC 패키징 물질 중에는 방사성 동위원소가 불순물로 일부 포함되어 있을 수 있습니다. 이로 인해 알파 입자가 방출되어 반도체 회로에 영향을 줄 수 있습니다. 이렇게 칩 내부에서 발생하는 알파에 대해서도 연구하고 있습니다.

그림 17. Pb-free Solder에서 방출되는 알파 에너지 스펙트럼

○ 대기, 우주, 태양 방사선

그림 18. 반도체 내부에서 에너지를 가진 입자에 의해 발생하는 현상의 메커니즘

우주공간에서뿐만 아니라 대기권 안에서도 반도체는 여러 종류의 방사선의 영향을 받아 오동작을 일으킬 수 있습니다. 우주 공간에서 오는 방사선은 대기권을 통과하면서 대부분 차단되지만 중성자와 같은 일부 방사선은 지표면까지 도달할 수 있습니다. 이러한 방사선이 반도체 내부를 통과하면서 전자와 정공(electron-hole pair)을 만들어내고 전류의 발생으로 이어지게 됩니다. 이때 발생한 전류에 의해 시스템의 상태가 변하게 되며 물리적인 데미지를 입은 것이 아니기 때문에 전원을 껐다 켜거나 값을 다시 쓰는 것으로 정상으로 동작하기 때문에 소프트한 에러(Soft Error)라고 정의합니다. 본 연구실은 이러한 현상의 원인 분석을 통해 신뢰성을 확보하기 위한 연구를 진행하고 있습니다.

■ 공동 연구

미국, 캐나다, 스페인, 중국 등의 학교 및 Cisco, Samsung, Hynix와 같은 국내외 회사들과 공동 연구를 통해 산업 현장에서 적용 가능한 연구를 지향하고 있습니다.

|

|

|

|

|

|

|